Contact: mketchen@octevue.com

Get temporal performance information at the device level early to avoid surprises at the system level later

While device level activity on today’s microelectronic chips takes place on the ps timescale, information on this activity is most

frequently deduced from the integrated performance of an aggregate system over a longer time period.

With this approach important features at the device level can be obscured or missed altogether,

only to emerge later in an exaggerated and detrimental way under certain operating conditions.

One way to avoid this ambiguity is to integrate on-chip measurement capability, either embedded in a system or through dedicated test structures,

that provides device level temporal information.

While device level activity on today’s microelectronic chips takes place on the ps timescale, information on this activity is most

frequently deduced from the integrated performance of an aggregate system over a longer time period.

With this approach important features at the device level can be obscured or missed altogether,

only to emerge later in an exaggerated and detrimental way under certain operating conditions.

One way to avoid this ambiguity is to integrate on-chip measurement capability, either embedded in a system or through dedicated test structures,

that provides device level temporal information.

Through much of his career at IBM Dr. Ketchen has worked with digital devices that switch on the ps timescale,

beginning with Josephson devices in the late 1970s and continuing on through today’s highly scaled CMOS devices and SFQ circuits.

He has been personally involved in development and application of a number of techniques for obtaining

time domain data at the individual device level. These techniques range from optoelectronic sampling with special probes,

to integrated on-chip samplers, to differencing techniques where sub-ps detail is revealed using on-chip circ

in combination with off the shelf measurement equipment. The concepts and generality of such approaches have proven

to be surprisingly time and technology independent!

1. Scanning SQUID sampler with 40-ps time resolution

Cui Z, Kirtley JR, Kratz PA, Watson CA, Rosernberg AJ, Gibson GW, Ketchen MB , Moler KA (2017). Review of Scientific Instruments, 88, 083703

2. Direct measurement of jitter in a JTL

Fung Y K-K, Gibson GW, Bulzacchelli JF, Polonsky S, Ketchen MB (2013). IEEE Transactions on Appl Sup 23: 1701405

3. CMOS latch metastability characterization at the 65-nm-technology node

Bhushan M, Ketchen MB, Das KK (2008).

Proceedings of the 2008 IEEE international conference on microelectronic test structures, 2008, pp 147-151

4. Measurement of thermal time constant in 65-nm PD-SOI technology with sub-ns resolution

Ketchen MB, Xiu K, Bhushan M (2007). Proceedings of the 2007 IEEE international SOI conference, 2007, pp 53-54

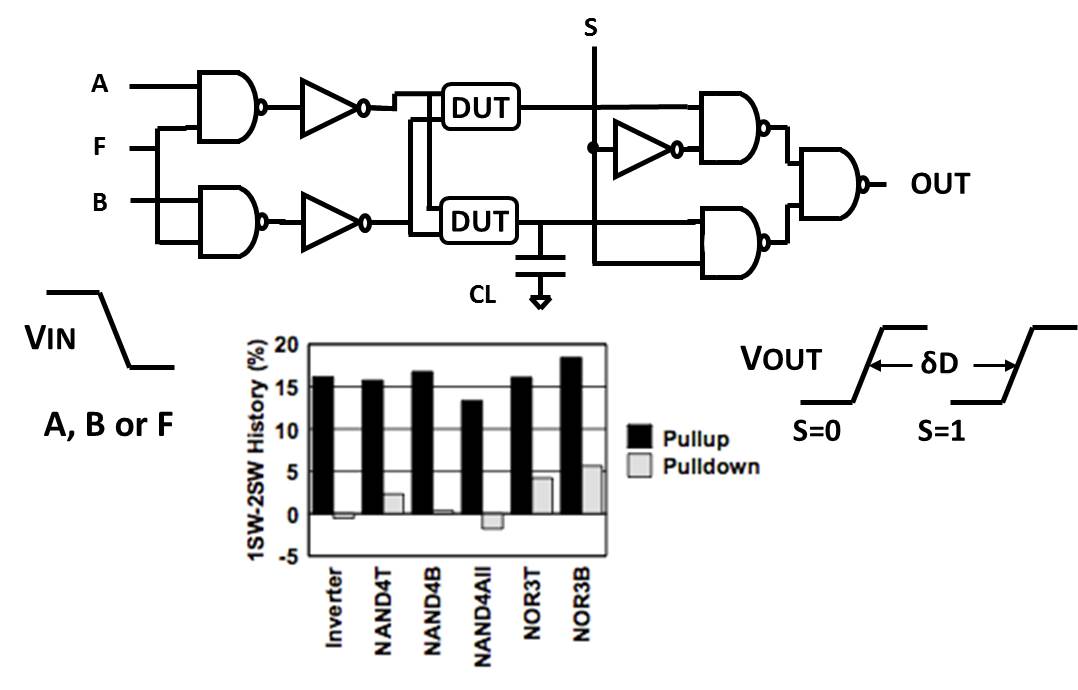

5. Circuit and technique for characterizing switching delay history effects in silicon-on-insulator logic gates

Ketchen MB, Bhushan M, Anderson CJ (2004).

Rev Sci Instrum 75:768-771

6. Generation of subpicosecond electrical pulses on coplanar transmission lines

Ketchen MB, Grischkowsky D, Chen TC, Chi C-C Duling III IN, Halas NJ, Halbout JM, Kash JA,Li GP (1986). Appl Phys Lett 48:751-753